|

•D™O®Ō•ő™ļAccusilicon clocks:

USB¨…≠Ī®Ō•ő™ļCrystek clocks:

点击§U载USB驱动

Amanero

combo 384

R-7 °]20īŕ°^™ļ∑sĮS© °G

1°A 10MHz时钟输§JĪĶ§f°A•i•H连ĪĶ•~≥°™ļ时钟发•ÕĺĻ°C

2°A FPGA数’u处≤zľ“¶°§…级为¶}¶ś处≤zľ“¶°°C

IISęH号¨O¶Í¶ś数’uľ“¶°°A®C个数’u≥£Ľ›≠n§@个时钟©PīŃ°A§@帧•™•k声ĻD数’uĽ›≠n64个时钟©PīŃ

°A®Ł®ž64个时钟©PīŃ稳©w© ™ļľv响°C

¶”¶}¶śľ“¶°•uĽ›≠n§@个时钟īN•i•H传输§ő处≤z•™•k声ĻD™ļ32¶ž数’u°A§j§jī£į™§F运¶ś处≤z≥tę◊•Bßů§£®Ł时钟稳©w© ™ļľv响°C

IIS输§J数’u(USB…OHDMI-IIS°^

§@输§JīN•ŖßY≥Q≠ę组¶®双32¶ž¶}¶ś数’u°CSPDIFęH号ł—调¶Z§]≥q过双24¶ž¶}¶ś数’u§Ť¶°įe®ž§U§@级处≤z°CDSD数’u

§]¨O§@输§JīN≠ę组¶®双64¶ž¶}¶ś数’u处≤z°C

经对§Ů≤‚ßv°A¶}¶ś处≤zľ“¶°•i•H•O声≠Ķßů≤Mī∑§§© °A动态ßů®ő¶”ßů®„ľ“拟®ż°C

3°A ∑sŐب[™ļ时钟ļř≤z设计°A时钟§uß@ßů稳©w

°A≥z©ķę◊ßůį™细节ßů§•īI°C

4°A DSD®Ō•ő内łm…›®B时钟≠ę∑sģ’对°A©ķ显ī£į™ľĹ©Ů™ļ≤Mī∑ę◊…O动态°C

5°A §šęýDOPľĹ©Ů°C

R-7•ő户∑P®Ł°G

https://www.head-fi.org/threads/new-audio-gd-r2r-7-flagship-resistor-ladder-dac.853902/page-180

6 Moon Reviews :

http://www.6moons.com/audioreviews2/audio-gd/1.html

R-2R DAC ™ļ…¨Į 点:

…¨点 :

1, R-2R

§£会将时钟ęH号转换®ž输•XęH号°C

2, R-2R §£Ī”∑P§_ jitter ¶ż

Delta-Sigma īN¨Ř当Ī”∑P°C

3,

R-2R™ļ输•XęH号电•≠™ļļŽ≠„ę◊į™§_Delta-Sigma .

Į 点 :

1, R2R

™ļ谐™i•ĘĮuę◊•i•HįĶ®ž¨Ř当ßC¶ż还§£ĮŗįĶ®ž∂HES9038

PRO (Delta-Sigma)®ļ样™ļßC谐™i•ĘĮu°C

2, Glitch

…OĪŤ阶电™ż™ļļŽę◊§£ģe©Ųł—决°C

•ę场§W¨y¶ś™ļR-2R设计:

无论¨ODIYģM•ů©ő¨O…D®Óę~°AR-2R§w经变Īo¨y¶ś°C

¶bßC…≤¶ž™ļDIY ģM•ů•ę场°A≥qĪ`™ļ设计¨O学习§FMSB旧¶≥ßř术°A¶ż仅ęOĮd§FęH号转换™ļ≥°§ņ¶”™Ŕ弃§F≠ž…DļŽßģ™ļ设计°C这Ōķ设计¨O≥q过数’u¶Í¶ś输§J®ž≤嶞ĪH¶sĺĻIC•h将数’u

转换®žľ“拟ęH号™ļ转换°A¨Oģŕ•Ľ无™kł—决R-2R™ļßř术难题°A这Ōķ设计™ļ© Įŗ¨OßĻ•Ģ®Ő赖ĪŤ阶电™ż™ļļŽę◊°C

¶bHi -End

•ę场™ļ…D®Óę~°A®Ō•ő§F¨Ř当ő`杂™ļßř术•hł—决R-2R¶s¶b™ļ问题°A从¶”达®žį™© Įŗ…O≠Ķ质°C

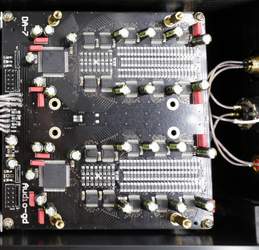

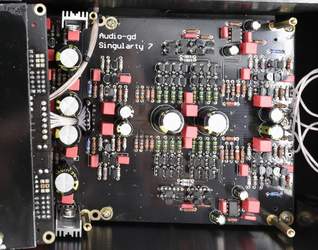

§@®«…Dģa®Ō•ő≤嶞ĪH¶sĺĻIC™ļ¶Í¶śĪĪ®Óľ“¶°°C§U图™ļ设计¨O®Ō•ő§FFPGA¶}¶śĪĪ®ÓĪŤ阶电™ż开关™ļ§Ť¶°°C¶}¶śĪĪ®Óľ“¶°°A®C§@bit™ļĪŤ阶电™ż开关≥£单独ĪĪ®Ó°A¶]¶Ļ®„¶≥∂Wį™≥tę◊

°]¶}¶śľ“¶°仅Ľ›1个时钟©PīŃ•h输•X©“¶≥数’u°A ¶Í¶śľ“¶°则Ľ›≠n

¶‹§÷8®ž24个时钟©PīŃ°^•h发įe©őßů∑s数’u°A¶}•i•H¶b•Ű¶ů时≠‘ßY时纠•Ņ数’u从¶”•O输•XęH号®„¶≥ßC•ĘĮuĮS© °Ał—决•—§_电™ż§Ĺģt§őGlitchĶ•§ř≠P™ļ问题°C

ĪŤ阶电™ż™ļļŽę◊:

ꋶh§H•u关§ŖĪŤ阶电™ż™ļļŽę◊°A

•L们¨›来R-2RīN¨O®ķ决§_电™ż™ļļŽę◊°C

现§Ķ°A24

bit§w¨O§@个标≠„°A¶ż•i®Ó≥y™ļ电™żļŽę◊¨Oß_•i•H达®ž24 bit°H

ßY®Ō¨O16 bit,

ļŽę◊≠n®D§w¨O1/66536°A ßY®Ō¨O 0.1% °]1/1000°^™ļ电™żļŽę◊°A¨OßĻ•Ģ§£®¨够™ļ°CīNļ‚¨O0.01%

°]1/10000°^°A§]®ŐĶM•ľĮŗ达®ž 16 bit™ļ≠n®D°Aßů§£≠n说¨O24 bit.

¶]¶Ļ电™ż™ļļŽę◊¶}§£¨Oł—决问题™ļ§Ť¶V°Cį≤¶p•@¨…§W¶≥0.00001%™ļ电™ż°AĮŗ达®ž24

bit™ļ≠n®D°A¶żĪŤ阶电™ż™ļ开关内™ż™ļ÷√ī≤© °A会将这个∂W级į™ļŽ≠„ę◊

™ļ…¨势ßĻ•Ģ©Ŕ•h°C

ßŕ们≠n从ßř术§Wł—决问题°A¶”§£¨O单凭ī£į™电™ż™ļļŽę◊°C¶żßŕ们®ŐĶM¶b产ę~§§®Ō•ő∂Wį™ļŽę◊™ļ电™ż°C

¨Ř当≠ę≠n™ļFPGA:

FPGA¨O•i编Ķ{™ļ逻辑阵¶CĺĻ•ů°C

现§Ķ°AFPGA§w应•ő¶b§£§÷ Hi-End级别™ļDAC产ę~§§°A

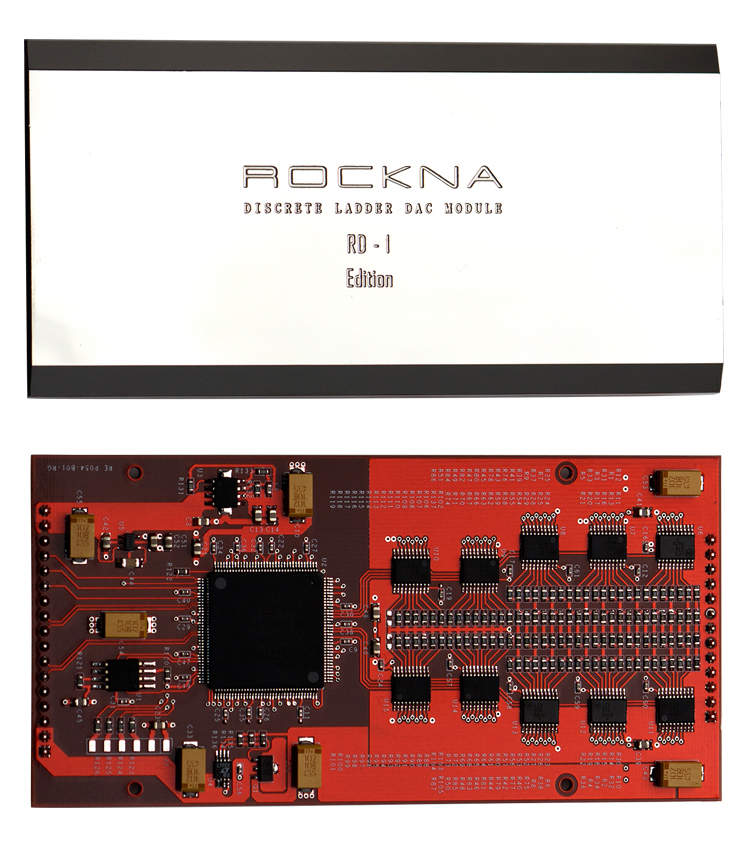

∂H¨y¶ś™ļROCKNA WAVEDREAM DAC.

FPGA内≥°™ļĶw•ů•¨ßĹ°A•i•H≥q过ő`杂™ļ软•ů•h设计…OĪ∆•¨°A¶}•BĶw•ů¨O•i•H≥q过软•ů™ļ§…级¶”Īo®ž§…级°C

当§…级©T•ů时°AĶw•ůīN会¶P时Īo®ž§…级°C这样™ļ设计®„¶≥¨Ř当į™™ļ灵¨°© °A•i•H≥q过软•ů§…级实现≠Ķ质™ļī£§…°AľW•[ßů¶hßů∑s™ļ•\Įŗ°A•H§ő•O产ę~•√远§£会ł®¶Z§_时•N°C

R-7没¶≥设计•Ű¶ů™ļ静≠Ķ开关•HęO证ęH号ę~质°C

责•Ű≠ę§j™ļFPGA:

1, 内ęōį™© ĮŗSPDIFł—调ĺĻ°A¶”§£™Ų•ő•ę场§W©T§∆ßC© Įŗ™ļSPDIFł—调™š§ý¶p

DIR9001, WM8805 and AK411X Ķ•.

2,

≠ę组时钟§őFIFOßř术°A输•X数’u•i•HļŽ≠„¶P®B®ž时钟§W°A©ŕ绝jitter.

3, 内ęō 2X, 4X

and 8X 数¶r滤™iĺĻ°A§ő4Ōķ§£¶Pļ‚™kNOSľ“¶°•i®—•ő户选择≥Ő贴¶X个§H§f®ż™ļ≠Ķ¶‚°C

•Ģ§ņ•Ŗ•ů输•X级:

ęH号经过≥Ő¶Z§@级¨Oľ“拟输•X级°A输•X级对DAC™ļ≠Ķ质ľv响¨O决©w© ™ļ°C¶A…¨®q™ļ数¶r电łŰ设计°A没¶≥§@个…¨®q™ļľ“拟输•X级设计°A≠Ķ质§]会变ĪoŐŚ®šī∂≥q°C

ľ“拟输•X级™ĹĪĶ连ĪĶ¶bDA

7

ľ“块¶Z≠Ī°A•Ģ≥°®Ō•ő过§’¶°§ł•ů°]ęDSMD°^°C

į™≥t™ļCAST©Ů§jĺĻ担•ŰęH号™ļ©Ů§j…O处≤z°ACAST©Ů§jĺĻ¨O没¶≥负§Ō馈™ļ设计°A•B§uß@§_电¨yęH号ľ“¶°°A¶”§£•≤∂H®š•L™ļ设计§@样°A将ęH号§Ōő`¶b电¨y…O电压间¶h¶ł变换°C

输•X™ļ缓冲ĺĻ级¨O单ļ›纯A类FET设计°A•B两组¶}联•H实现ßůßC™ļ输•X™żß‹°C

总¶”®•§ß°A输•X级¨O§uß@§_纯A类™ļ状态°AßĻ•Ģ没¶≥负§Ō馈°A •H•i•H≠ę现纯净…OĻGĮu™ļ声≠ĶęH号°C

DAC内ęō•|个OPA运©Ů担•Ű™Ĺ¨y¶Ý™A•\Įŗ°A这样DACīN无Ľ›ĹʶX电ģe§]•i•H•ŅĪ`§uß@°AŃ◊ßK§F电ģe产•Õ™ļ≠Ķ¨V°C

¶bDA

ľ“块¶Z™ļ©“¶≥ęH号≥qĻD°A没¶≥®Ō•ő•Ű¶ů开关§ł•ů•H实现≥ŐĮu≥Ő纯™ļ≠Ķ质ģń™G°C

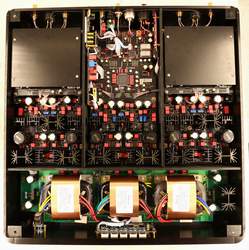

强§j™ļ电∑Ĺ设计:

DAC 内ęō¶≥3个Rę¨变压ĺĻ°A总•\≤v达®ž 130W°A对数¶r≥°§ņ°A

•™•k声ĻD™ļľ“拟≥°§ņ进¶ś§ņ÷√独•Ŗ®—电°C

内ęō¶≥20组纯A类™ļ稳压电∑ŧő3组线© 电∑Ĺ®—电®ž¶U§£¶P≥°§ņ°C

•Ģ≥°电∑Ĺ≥£®„¶≥∂Wį™≥t§ő∂WßCĺł≠Ķ™ļĮS© °C

•¨ßĹ

:

DAC®Ō•ő5MMęp™ļ铝™O•h§ņĻj开数¶r≥°§ņ°A•™…O•k声ĻDľ“拟≥°§ņ§ő变压ĺĻ≥°§ņ°A•HŃ◊ßK•¶们§ß间™ļ¨Ř§¨§z ū°C

•™•k声ĻD™ļľ“拟≥°§ņ®Ō•ő对称•¨ßŧņ•¨§_数¶r≥°§ņ两侧°A®„¶≥¨Ř¶P™ļęH号线长ę◊…O∂Z÷√°A•O≠Ķ质ßůļŽ≠„°C

DA 7 ľ“块¶w装®ž两块铝™O§§间•HŃ◊ßK®š•L电łŰ™ļ§z ū°C

Ńcő`™ļ•¨ßĹ…O¶w装§u艺•u¶]为§F≠Ķ质ßů≤Mī∑纯Įu°A≠Iīļßů…r静°A≠Ķ场ßů宽广°C

|